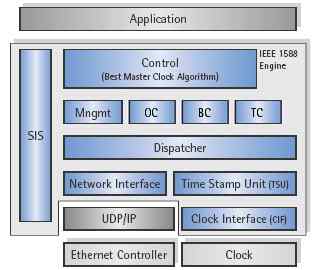

IP核模块实现了IEEE1588-2008标准中的高精度同步时钟规范。

在本地实时时钟(local real-time clock)和主时钟(master clock)之间有一个时钟调节器,该调节器用来提供了IEEE1588标准中报文的高精度时间戳。如果用户使用的CPU不在IEEE1588标准的支持列表中,那么获取高精度时间戳的方法只能通过软件时间戳(software time stamping)或者使用外部的符合IEEE1588标准的配有时间戳单元(time stamping unit)的实时时钟。若时间戳是有由软件生成,则时钟同步精度应该在数十微秒到毫秒之间。

如果时间戳是由硬件FPGA实现的,则时间戳的生成精度与FPGA内部时钟一致,范围在20-50纳秒之间,其具体值依赖于FPGA内部时钟的频率。介于主时钟(master clock)和从时钟(slave clock)之间的时钟同步(timer synchronization)精度可以精确到几十纳秒的范围之内。

使用触发器单元(trigger unit),改变数字输入信号就能通过时间戳来精确捕获时序。前提是需要一个能够精确生成给定起始时间和频率的时钟输出信号。

IEEE1588 IP核将用于如下环境:

- FPGA内部的软核CPU(比如Altera NIOS)运行IEEE1588协议软件的环境中(IEEE1588设备被当做片上解决方案)

- 外部CPU运行IEEE1588协议软件和应用软件的环境中

特性

- 通过软件来配置和调节实时时钟

- 触发器单元(trigger unit)提供外部输入信号的时间戳

- 外部输出信号的触发基于可配置的定时器

- GMII接口用于流入和流出的同步消息检测(MII和RMII的转化器包括在配货范围内)

- 支持IEEE1588版本1(IEEE1588-2002)和版本2(IEEE1588-2008)

- FPGA模式和软件模式都支持IPv4、IPv6和IEEE802.3(第2层)消息时间戳

- 标准的地址/数据总线接口

- 缓冲器存储时间戳信息和可能带有中断消息的附加信息

- 可能变化的外部时钟频率

- 有外部时钟精度测量PPS信号

配货内容

- Altera Mega Core(全授权或者OpenCore+)

- 加密VHDL代码

- C源码级的设备驱动和示例应用

- IXXAT的工业以太网模块(硬件评估套件)

- 使用手册

- 快速使用指南

- 45天的技术支持(从配送日起算)

技术数据

- Altera逻辑单元数量:大约2000

- 精度:

+/-150ns(外部时钟频率50MHz)

+/-75ns(外部时钟频率80MHz) - 加密IP核(Altera FPGA)

附加服务

(不包含在供货内容内)

维护合同(Maintenance contract)

IXXAT针对配货中的软件包提供维修服务。维修服务包括:

- 免费升级和故障排除

- 技术支持

IXXAT负责编写、实现和测试IEEE1588 IP核到客户硬件或应用。

IEEE 1588 PTP协议软件

IEEE 1588协议软件便于客户在IEEE1588 IP核基础上,简洁、迅速的开发符合IEEE 1588标准的设备。

收藏灵猫网

收藏灵猫网

12522120

12522120