FEATURES:

-

32-bit timing reference counter

-

25 ns timing resolution

-

32-bit input pulses counter

-

Hardware or software start and stop signals

-

Selectable edge or level of the start and stop signals

-

Gate signal for timing counter and/or for input pulses

-

PCI interrupt generation at the end of measurement

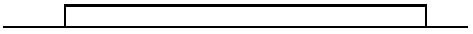

Principle of the frequency operating mode.

The counting period can be defined in a programming manner. The resolution of the counting period is 25 ns. The counting may be started by a program or by an external signal.

The block counts the rising edges of the input signal. If it is needed to count the falling edges a program can invert the input signal at the input of the block.

Optionally a gate input signal can be applied to stop the counting of the pulses of the input signal as well as to stop the counting of the counting period. The source of the gate signal may be a program or an external signal. The active level of the gate signal may be set by a program.

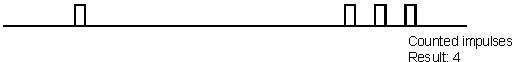

Reference frequency

Counting period

Input signal

Gate signal Active high

Principle of the gate signal.

When the counting period terminates the result is ready. Optionally a PCI interrupt may be generated at counting completion.

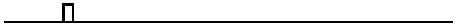

In the pulse width mode the block counts the time span between the start and stop conditions. The resolution of the time measurement is 25 ns. The start and stop conditions are selected in a programming way as rising or falling edges of the input signal. So the block may be applied to measure the duration of the “H” input state (start signal generated by the rising edge and stop generated by the falling edge), the duration of the “L” state of the input signal (start and stop conditions generated by the falling and rising edges respectively) or to measure the period of the input wave (both stop and start signals generated by the rising or falling edges).

The counting may be gated as in the case of the frequency measurement mode. As well a PCI interrupt may be optionally generated when the counting is completed.

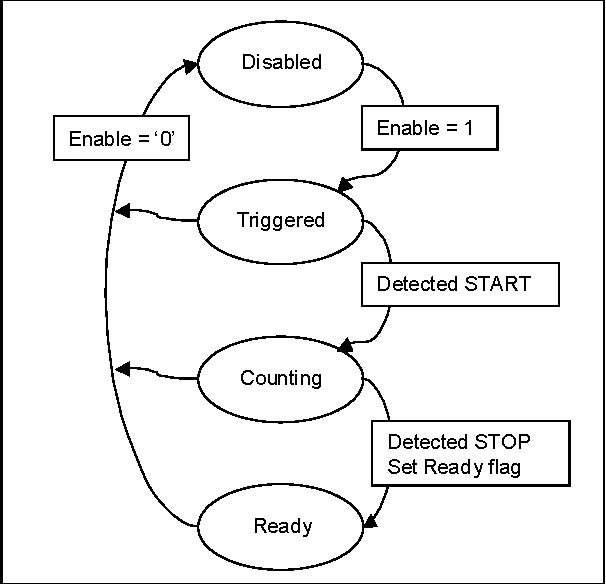

The FreqM block is implemented as a Finite State Machine (FSM). The FSM contains four states: Disabled, Triggered, Counting and Ready. The state flow is presented below.

Counting period

Start signal

Stop signal

Principle of the period measurement.

Current state of the FSM may be read by a program.

FSM of the FreqM block.

If the Enable flag is cleared the block remains in the Disabled state. When the Enable changes from 0 to 1 the state changes to Triggered. In the Triggered state the blocks waits for the start counting condition. In the frequency measurement mode the start condition comes from the software or hardware start signal. In the pulse width measurement mode a proper edge of the input signal has to be detected to generate the start counting signal. After the start counting condition appears the blocks moves to the Counting state. In the frequency mode the block counts the periods of the input signal and in the pulse width mode the clock periods are counted. The block switches into the Ready state when the stop condition is detected. In the frequency mode the stop condition is generated if the timer reaches zero value.

In the pulse width mode the stop is generated by a proper edge of the input signal.

CUSTOMISATION: the number of available blocks, the length of the time reference and pulse counters and the assignment to the board connectors.